7448 BCD TO 7-SEGMENT DECODER

Description:

The SN54 /74LS48 is a BCD to 7-Segment Decoder consisting of NAND

gatesinput buffers and seven AND-OR-INVERT gates. Seven NAND gates

and one driver are connected in pairs to make BCD data and its complement

available to the seven decoding AND-OR-INVERT gates. The remaining

NAND gate and three input buffers provide lamp testblanking input/rippleblanking input for the LS48.

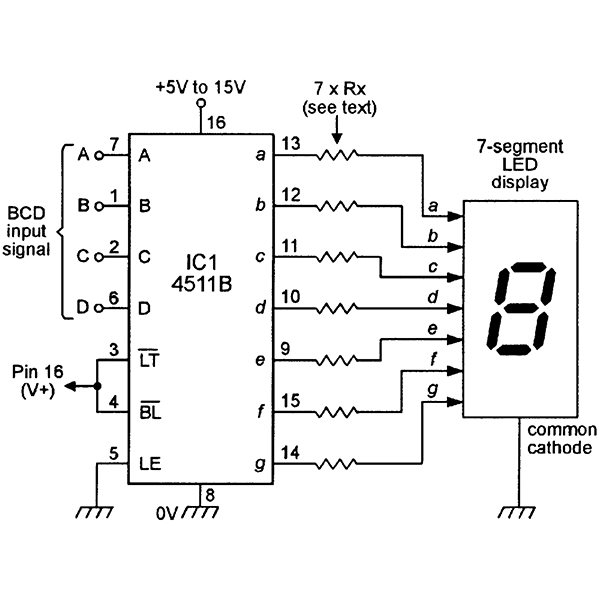

The circuit accepts 4-bit binary-coded-decimal (BCD) anddepending on

the state of the auxiliary inputsdecodes this data to drive other components.

The relative positive logic output levelsas well as conditions required at the

auxiliary inputsare shown in the truth tables.

The LS48 circuit incorporates automatic leading and/or trailing edge

zero-blanking control (RBI and RBO). Lamp Test (LT) may be activated any

time when the BI/RBO node is HIGH. Both devices contain an overriding

blanking input (BI) which can be used to control the lamp intensity by varying

the frequency and duty cycle of the BI input signal or to inhibit the outputs.

Lamp Intensity Modulation Capability (BI/RBO)

Internal Pull-Ups Eliminate Need for External Resistors

Input Clamp Diodes Eliminate High-Speed Termination Effects

Kit include:

1X 7448 BCD TO 7-SEGMENT DECODER

Documents:

Related Products

subscribe to our weekly newsletter